# **Timestamp Synchronization of Concurrent Events**

Daniel Becker

Forschungszentrum Jülich GmbH Institute for Advanced Simulation (IAS) Jülich Supercomputing Centre (JSC)

# **Timestamp Synchronization** of Concurrent Events

Daniel Becker

Schriften des Forschungszentrums Jülich IAS Series

Bibliographic information published by the Deutsche Nationalbibliothek. Die Deutsche Nationalbibliothek lists this publication in the Deutsche Nationalbibliografie; detailed bibliographic data are available in the Internet at <a href="http://dnb.d-nb.de">http://dnb.d-nb.de</a>

Cover Illustration: nemadesign GbR, Stuttgart

Publisher Forschungszentrum Jülich GmbH

and Distributor: Zentralbibliothek, Verlag

D-52425 Jülich

phone: +49 2461 61-5368 · fax: +49 2461 61-6103

e-mail: zb-publikation@fz-juelich.de Internet: http://www.fz-juelich.de/zb

Cover Design: Grafische Medien, Forschungszentrum Jülich GmbH

Printer: Grafische Medien, Forschungszentrum Jülich GmbH

Copyright: Forschungszentrum Jülich 2010

Schriften des Forschungszentrums Jülich

IAS Series Volume 4

D 82 (Diss., RWTH Aachen, Univ., 2009)

ISSN 1868-8489 ISBN 978-3-89336-625-5

The complete volume is freely available on the Internet on the Jülicher Open Access Server (JUWEL) at http://www.fz-juelich.de/zb/juwel

Persistent Identifier: urn:nbn:de:0001-2010051916

Resolving URL: http://www.persistent-identifier.de/?link=610

Neither this book nor any part may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying, microfilming, and recording, or by any information storage and retrieval system, without permission in writing from the publisher.

#### **Abstract**

Supercomputing is a key technological pillar of modern science and engineering, indispensable for solving critical problems of high complexity. However, to effectively utilize the enormously complex large-scale computer systems available today, scientists and engineers need powerful and robust software development tools. One technique widely used by such tools is event tracing with a broad spectrum of applications ranging from performance analysis, performance prediction and modeling to debugging. In particular, event traces are helpful in understanding the performance behavior of parallel programs since they allow the in-depth analysis of communication and synchronization patterns. The accuracy of such analyses depends on the comparability of timestamps taken on different processors and may be adversely affected by non-synchronized clocks leading to inaccurate relative event timings. Such inaccuracies may cause a given interval to appear shorter or longer than it actually was, or introduce violations of the logical event order, which requires a message to be received only after it has been sent. Inconsistent trace data may not only lead to false conclusions, for instance, when the impact of communication patterns is quantified, but may also confuse the user of trace-visualization tools by causing message arrows to point backward in time-line views. Even more strikingly, trace-analysis tools may also cease to work in a satisfactory manner if they rely on the correct order to function properly. Although linear offset interpolation can restore the consistency of the trace data to some degree, time-dependent drifts and other inaccuracies may still disarrange the original sequence of events, as shown in a study conducted as a part of this Ph.D. thesis.

The already familiar controlled logical clock algorithm accounts for such violations in pointto-point communication by shifting message events in time as much as needed while trying to preserve the length of local intervals. This algorithm is, however, not suitable for realistic applications because (i) it ignores collective and shared-memory operations and (ii) as a serial algorithm it offers only limited scalability. This thesis addresses these shortcomings by extending the algorithm to restore event semantics related to collective and shared-memory operations and by parallelizing the extended version to make it suitable for large-scale systems including computational grids. The basic idea behind the semantic extension is to consider collective and shared-memory operations as being composed of multiple point-to-point messages, taking the semantics of the different flavors of these operations into account. In order to accomplish the correction in a scalable way, both distributed memory and parallel processing capabilities are exploited by processing separate local trace files in parallel and replaying the original communication on as many CPUs as were used to execute the target application itself. To employ the replay mechanism in computational grids, this work also defines the necessary infrastructure to accurately measure clock offsets in distributed environments with hierarchical networks.

The methodology was evaluated in practice by integrating the extended and parallelized algorithm into the Scalasca trace-analysis framework and applied to traces of realistic applications taken on single cluster systems and computational grids. The thesis shows that the algorithm eliminates inconsistent timings of concurrent events while only marginally changing the length of intervals between local events – even if wide-area communication is involved. Scalability is demonstrated with up to 4,096 application processes.

## Kurzfassung

Supercomputing ist eine Schlüsseltechnologie moderner Wissenschaft und Technik, die zur Beantwortung schwieriger und komplexer Fragen unersetzlich ist. Zur effizienten Nutzung der neuesten Supercomputersysteme benötigen Wissenschaftler und Ingenieure mächtige und robuste Softwarewerkzeuge. Dabei ist das Aufzeichnen von Laufzeitereignissen in Ereignisspuren eine etablierte Technik sowohl zur Leistungsanalyse, Leistungsvorhersage und Modellierung als auch zum Debugging. Grund für die besondere Eignung der Ereignisspuren zur Untersuchung des Leistungsverhaltens paralleler Programme ist ihre Fähigkeit, die Analyse von Kommunikations- und Synchronisationsmustern zu ermöglichen. Die Genauigkeit dieser Untersuchungen hängt dabei von der Vergleichbarkeit der Zeitstempel einzelner nebenläufiger Ereignisse ab und kann daher durch nicht synchrone Prozessoruhren, die ungenaue Zeiten liefern, vermindert werden. Solche Ungenauigkeiten können sowohl die Länge eines gegebenen Intervalls kürzer oder länger erscheinen lassen, als auch zu Verletzungen der logischen Ereignisabfolge in Ereignisspuren führen, welche verlangt, dass eine Nachricht erst empfangen wird, nachdem sie gesendet wurde. Inkonsistente Ereignisspuren können somit nicht nur zu falschen Schlussfolgerungen, zum Beispiel während der Quantifizierung des Einflusses einzelner Kommunikationsmuster führen, sondern auch die Anwender von Visualisierungswerkzeugen verwirren, indem rückwärts gerichtete und somit in die Vergangenheit weisende Nachrichtenpfeile angezeigt werden. Besonders auffällig sind dabei diejenigen Analysewerkzeuge, die ihre Bearbeitung sogar gänzlich abbrechen, da sie die korrekte logische Abfolge von Ereignissen zur exakten Verarbeitung voraussetzen. Obwohl eine lineare Interpolation des Uhrenabstandes die Konsistenz der Ereignisspuren zu einem gewissen Grad wiederherstellen kann, können zeitabhängige Uhrenabweichungen und weitere Ungenauigkeiten die ursprüngliche Abfolge von Ereignissen ändern, wie in einer Studie als Teil dieser Doktorarbeit gezeigt wird.

Der schon bekannte Algorithmus der geregelten logischen Uhr korrigiert solche Verletzungen in Punkt-zu-Punkt Kommunikationen durch eine ausreichende zeitliche Verschiebung von Nachrichtenereignissen, wobei versucht wird, die Intervalllänge zwischen lokalen Ereignissen zu erhalten. Dieser Algorithmus ist jedoch für realistische parallele Programme nicht geeignet, weil er (i) kollektive Operationen sowie Operationen, die einen gemeinsam genutzten Speicherbereich ansprechen, ignoriert und (ii) als serieller Algorithmus nur eingeschränkte Skalierbarkeit aufweist. Diese Arbeit behebt die beschriebenen Limitierungen zum einen durch die Erweiterung des Algorithmus zur Wiederherstellung von Ereignissemantiken in den oben angeführten Operationen und zum anderen durch die Parallelisierung des erweiterten Algorithmus zur Anwendung auf Supercomputern und Grids. Der Semantikerweiterung liegt die Idee zugrunde, die genannten Operationen zusammengesetzt aus einzelnen Punkt-zu-Punkt Nachrichten aufzufassen und hierbei die verschiedenen Arten dieser Operationen zu berücksichtigen. Um die Korrektur skalierbar auszuführen, werden der verteilte Speicher und die parallelen Rechenressourcen zum einen durch eine parallele Verarbeitung einzelner lokaler Ereignisspuren und zum anderen durch das Nachspielen der ursprünglichen Kommunikation der Zielanwendung ausgenutzt. Um das beschriebene Verfahren auch in Grids einzusetzen, definiert die vorliegende Arbeit die notwendige Infrastruktur zur genauen Messung des Uhrenabstandes in verteilten Umgebungen mit hierarchischen Netzwerken.

Die Methodik wird evaluiert anhand der Integration des erweiterten und parallelisierten Algorithmus in die Leistungsanalyseumgebung Scalasca und deren Anwendung auf Ereignisspuren realistischer paralleler Programme, die auf verschiedenen Clustern und Grids aufgezeichnet wurden. Die vorliegende Arbeit zeigt dabei auf, dass der Algorithmus inkonsistente Intervalle beseitigt und zeitgleich die Länge von Intervallen zwischen lokalen Ereignissen nur marginal ändert – selbst wenn Weitverkehrsnetze eingesetzt werden. Zudem wird die Skalierbarkeit mit bis zu 4.096 Prozessoren gezeigt.

## **Acknowledgments**

I would like to thank Prof. Dr. Dr. Thomas Lippert, Director of the Jülich Supercomputing Centre, for giving me the opportunity to carry out my PhD project in his excellent and supportive research environment. This project would have never been possible without the enthusiastic supervision and guidance of my advisor Prof. Dr. Felix Wolf, to whom I owe a deep debt of gratitude. Moreover, I thank Prof. Dr. Christian Bischof and Prof. Dr. Michael Resch for serving as second referees. I am also grateful to Prof. Dr. Jack Dongarra for hosting me at the University of Tennessee, Dr. David Klepacki for creating the opportunity of a visiting research studentship at the IBM T. J. Watson Research Center, Prof. Dr. Jesus Labarta for supporting me at the Barcelona Supercomputing Centre, Dr. Patrick Worley for supporting me at the Oak Ridge National Laboratory, and Dr. Rolf Rabenseifner for introducing me to the controlled logical clock algorithm.

Thanks are due to colleagues at the Jülich Supercomputing Centre for numerous stimulating discussions, help with experimental setup, and general advice. I would especially like to acknowledge the invaluable assistance of Dr. Markus Geimer, when technical help was necessary, and Wolfgang Frings along with Morris Riedel, without whom the Grid would have been much cloudier. Not to be forgotten, thanks are due to my PhD colleagues for their help and support in myriad situations.

Finally, I am grateful to all my friends for being my surrogate family for so many years in various phases of my life and for their continuing moral support. Although unfair to mention just a few names, I would like to specially thank Vanessa along with Marco, Thomas, Tina, and Tom for just being there. Last but by no means least, I shall be forever indebted to my parents and family for their unshakeable faith, absolute support, and unstinting encouragement when all else failed and it was most required.

Daniel Becker December 2009

Causarum enim cognitio cognitionem eventorum facit.

CICERO, TOPICA 67

# **Contents**

| Li | st of                    | Figures                                                                                                     | ΧV                    |

|----|--------------------------|-------------------------------------------------------------------------------------------------------------|-----------------------|

| Li | st of                    | Tables                                                                                                      | xvii                  |

| 1  | 1.1<br>1.2<br>1.3<br>1.4 | Parallel Computers                                                                                          | 1<br>1<br>3<br>4<br>5 |

|    | 1.5                      | Timestamp Synchronization                                                                                   | 13                    |

| 2  | <b>Pro</b> (2.1          | Classification                                                                                              | <b>17</b><br>17       |

|    | 2.2                      | 2.1.1 Clock Types                                                                                           | 17<br>19<br>19        |

|    |                          | 2.2.1 Event Trace Generation         2.2.2 Accuracy Requirements         2.2.3 Implications of Inaccuracies | 19<br>20<br>21        |

|    | 2.3                      | Linear Offset Interpolation                                                                                 | 23                    |

|    | 2.4<br>2.5               | Sources of Inaccuracy                                                                                       | 24<br>25              |

|    | 2.6                      | 2.5.1 Clock Deviations                                                                                      | 26<br>29<br>32        |

| 3  |                          | ck Synchronization                                                                                          | 35                    |

| 3  | 3.1                      | Network-based Synchronization                                                                               | 35                    |

|    | 3.2<br>3.3               | Offset Interpolation                                                                                        | 35<br>36              |

|    | 3.4                      | Logical Synchronization                                                                                     | 38<br>40              |

|    | 3.5                      | Summary                                                                                                     |                       |

| 4  | <b>Con</b> 4.1           | Itrolled Logical Clock Rationale                                                                            | <b>41</b>             |

|    | 4.1                      | Rationale                                                                                                   | 41                    |

|    | 4.3                      | Backward Amortization                                                                                       | 47                    |

#### Contents

| Re | eferer            | nces                                                          | 109      |

|----|-------------------|---------------------------------------------------------------|----------|

| 8  | Sun               | nmary and Outlook                                             | 105      |

|    | 7.4               | Summary                                                       | 102      |

|    |                   | 7.3.3 Wide-Area Communication                                 | 100      |

|    |                   | 7.3.2 Message Passing Combined with Shared Memory             | 96       |

|    |                   | 7.3.1 Message Passing                                         | 89       |

|    | 7.3               | Logical Synchronization                                       | 88       |

|    | 7.2               | Hierarchical Offset Measurement                               | 86       |

|    |                   | 7.1.3 National Grid Service                                   | 84       |

|    |                   | 7.1.2 The Viola Metacomputer                                  | 82       |

|    | /.1               | 7.1.1 Cluster Systems                                         | 81       |

| ′  | <b>⊏хр</b><br>7.1 | erimental Evaluation Experimental Setup                       | 81       |

| 7  | Evn               | orimontal Evaluation                                          | 81       |

|    | 6.7               | Summary                                                       | 79       |

|    |                   | 6.6.2 Hierarchical Offset Measurement                         | 77       |

|    |                   | 6.6.1 Metacomputing Scenario                                  | 76       |

|    | 6.6               | Wide-Area Communication                                       | 76       |

|    | 6.5               | MPI Combined with OpenMP                                      | 73       |

|    |                   | 6.4.2 Piece-Wise Correction                                   | 71       |

|    | U. <del>T</del>   | 6.4.1 Backward Replay                                         | 70       |

|    | 6.4               | Backward Amortization                                         | 69       |

|    | 6.3               | Logical Clock with Forward Amortization                       | 67       |

|    | 6.2               | Integration with Scalasca                                     | 66       |

|    |                   | 6.1.1 Replay-Based Trace Analysis                             | 63<br>64 |

|    | 6.1               | Parallel Trace Analysis                                       | 63<br>63 |

| 6  |                   | allel Synchronization                                         | 63       |

| ^  | D                 | allal Comahannination                                         |          |

|    | 5.4               | Summary                                                       | 61       |

|    |                   | 5.3.2 Backward Amortization                                   | 60       |

|    |                   | 5.3.1 Logical Clock with Forward Amortization                 | 59       |

|    | 5.3               | Shared-Memory Event Semantics                                 | 58       |

|    |                   | 5.2.2 Backward Amortization for Collectives                   | 58       |

|    | 5.2               | 5.2.1 Logical Clock with Forward Amortization for Collectives | 56       |

|    | 5.2               | Collective Message-Passing Event Semantics                    | 56       |

| 3  | 5.1               | Basic Principle                                               | 51<br>51 |

| 5  | ۸۱۵               | prithmic Extensions                                           | 51       |

|    | 4.4               | Limitations                                                   | 48       |

|    |                   |                                                               |          |

# **List of Figures**

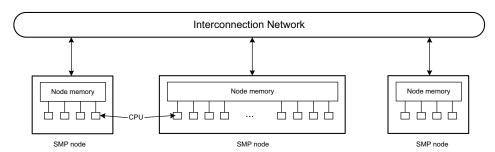

| 1.1  | Schematic view of a cluster                                                                   | 2  |

|------|-----------------------------------------------------------------------------------------------|----|

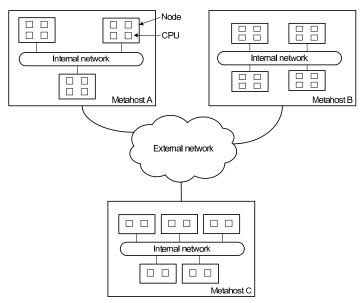

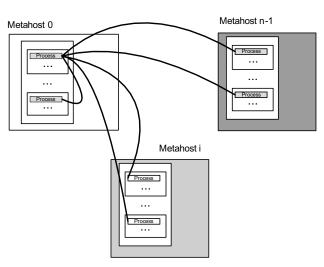

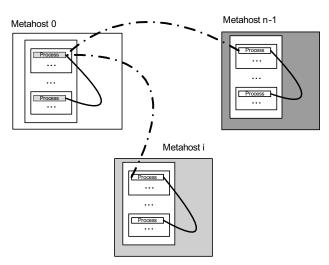

| 1.2  | Schematic view of a metacomputer                                                              | 4  |

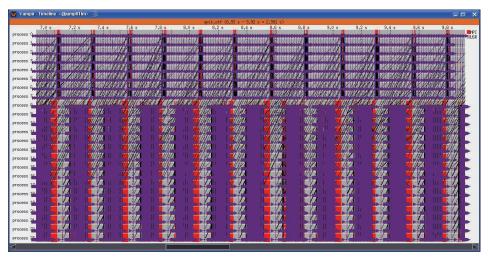

| 1.3  | Graphical trace browser Vampir: Time-line visualization of an application's                   |    |

|      | runtime behavior.                                                                             | 6  |

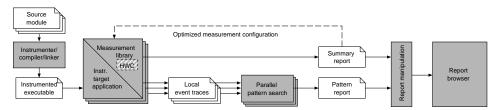

| 1.4  | Schematic overview of the performance data flow in Scalasca                                   | 7  |

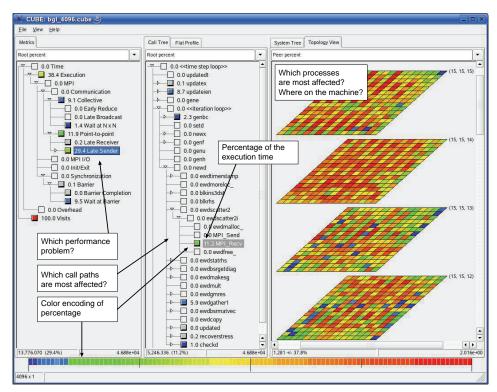

| 1.5  | Scalasca's trace-analysis report                                                              | 8  |

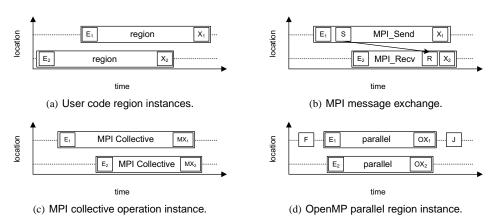

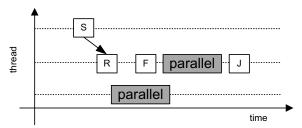

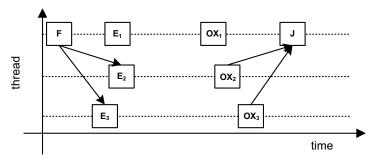

| 1.6  | Typical event sequences according to the Scalasca event model                                 | 11 |

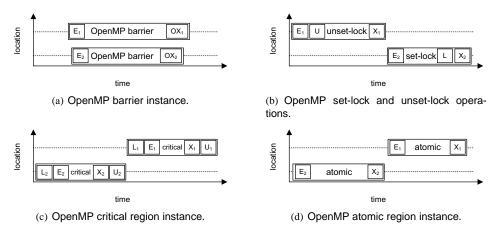

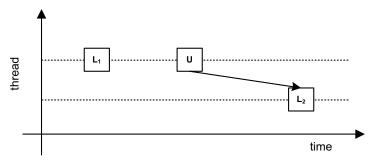

| 1.7  | Typical event sequences inside OpenMP parallel regions                                        | 12 |

| 1.8  | Time-line visualization of a message in backward direction                                    | 13 |

| 1.9  | Non-linear offsets of physical clocks                                                         | 14 |

| 2.1  | Two clocks with both an initial offset and different but constant drifts                      | 18 |

| 2.2  | Implications of inaccurate timestamps for message-passing event semantics                     | 21 |

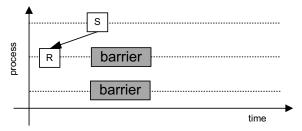

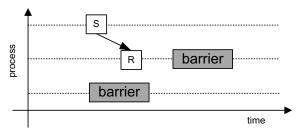

| 2.3  | Implications of inaccurate timestamps for shared-memory event semantics                       | 22 |

| 2.4  | A violation of OpenMP barrier semantics                                                       | 23 |

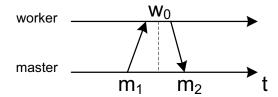

| 2.5  | Cristian's probabilistic remote clock reading technique                                       | 24 |

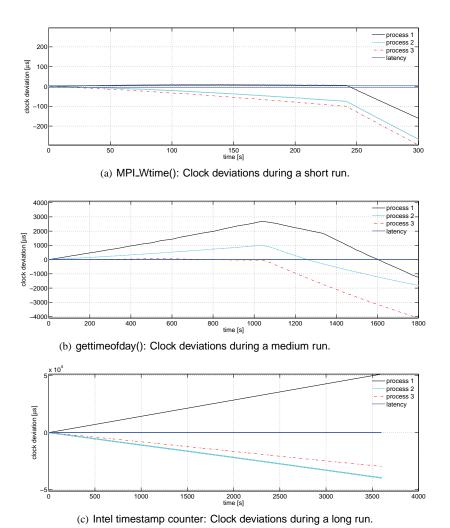

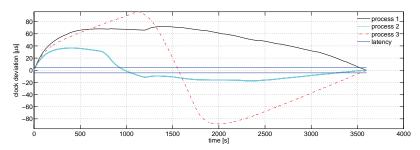

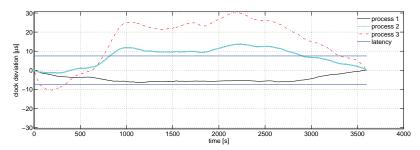

| 2.6  | Xeon cluster: Measured clock deviations of different timers during short,                     |    |

|      | medium, and long measurement runs after an initial offset alignment                           | 27 |

| 2.7  | Measured clock deviations of two different hardware clocks and gettimeof-                     |    |

|      | day() during long runs after linear offset interpolation                                      | 28 |

| 2.8  | Measured clock deviations after linear interpolation during a short run on the                |    |

|      | Xeon cluster                                                                                  | 29 |

| 2.9  | Xeon cluster: Percentage of messages with the order of send and receive events being reversed | 30 |

| 2.10 | Intel Itanium node: Percentages of parallel regions in an OpenMP benchmark                    |    |

|      | program exhibiting clock condition violations                                                 | 31 |

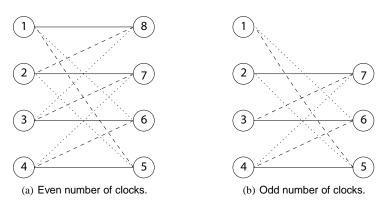

| 3.1  | Communication scheme including edge-coloring for pair-wise offset measure-                    |    |

|      | ments among even and odd numbers of clocks [29]                                               | 36 |

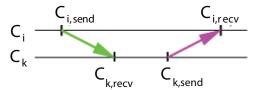

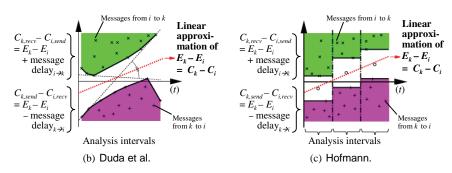

| 3.2  | Algorithms that calculate the clock errors through the differences of message                 |    |

|      | transfer times                                                                                | 37 |

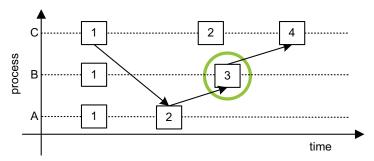

| 3.3  | Lamport's discrete logical clock                                                              | 39 |

| 4.1  | Backward and forward amortization in the controlled logical clock algorithm.                  | 44 |

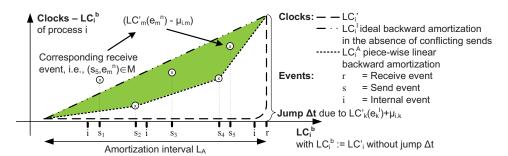

| 4.2  | Piecewise process-local linear correction as backward amortization                            | 48 |

| 4.3  | Implications of corrections based on point-to-point event semantics for collec-               | 40 |

|      | tive message-passing (MPI) event semantics                                                    | 49 |

#### **List of Figures**

| 4.4                                    | Implications of restoring point-to-point event semantics for shared-memory (OpenMP) event semantics                                                                                                                                                                                                                                                                                                           | 50                               |

|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

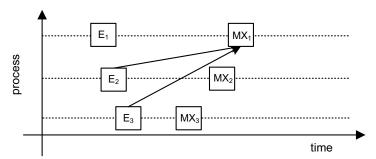

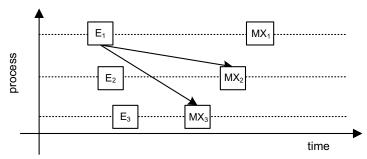

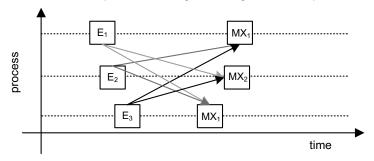

| 5.1<br>5.2                             | MPI collective operation event semantics                                                                                                                                                                                                                                                                                                                                                                      | 53<br>54                         |

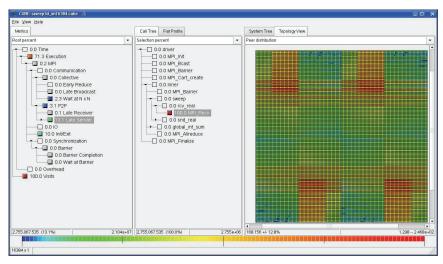

| 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6 | Scalasca's pattern search.  Trace-analysis report visualization and exploration in Scalasca.  Parallel trace-analysis process.  Time lines of two processes exchanging messages.  Backward amortization: Determination of the piece-wise linear correction.  Example of the trace-analysis report including grid patterns.  Flat offset measurements between each worker process and a single master process. | 65<br>66<br>67<br>71<br>72<br>77 |

| 6.8                                    | Hierarchical offset measurements between each local worker process and their local master                                                                                                                                                                                                                                                                                                                     | 79                               |

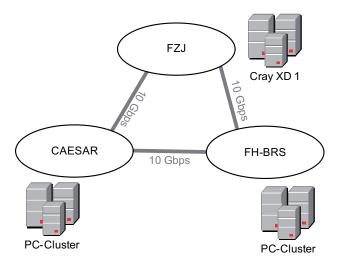

| 7.1                                    | Network topology of the Viola grid                                                                                                                                                                                                                                                                                                                                                                            | 83                               |

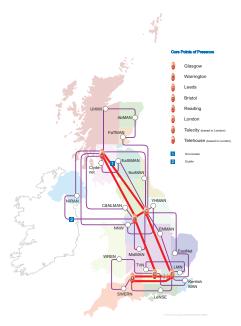

| 7.2                                    | Network topology of the Janet backbone [57]                                                                                                                                                                                                                                                                                                                                                                   | 84                               |

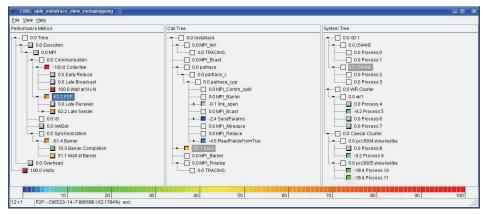

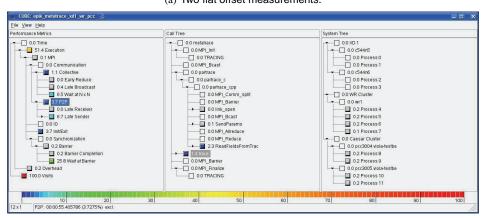

| 7.3                                    | Analysis reports calculated based on timestamps synchronized with flat offset measurements or hierarchical offset measurements                                                                                                                                                                                                                                                                                | 88                               |

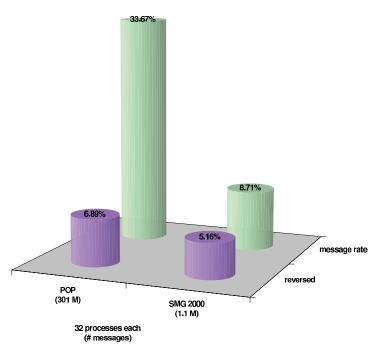

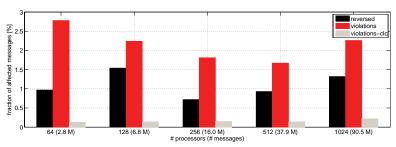

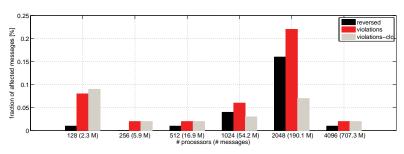

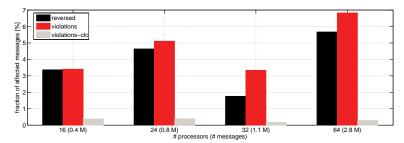

| 7.4                                    | Message statistics before and after applying the CLC algorithm for message-                                                                                                                                                                                                                                                                                                                                   | 0.0                              |

| 7.5                                    | passing applications                                                                                                                                                                                                                                                                                                                                                                                          | 90                               |

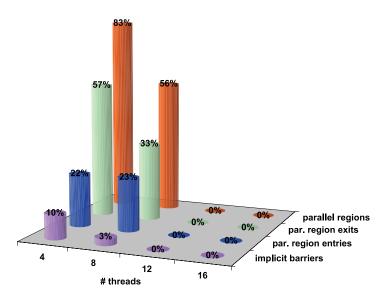

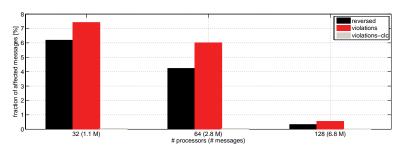

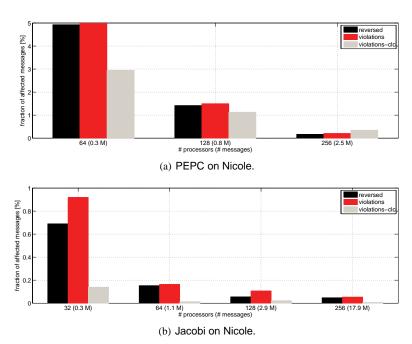

| 7.6                                    | Message statistics before and after applying the CLC algorithm to hybrid                                                                                                                                                                                                                                                                                                                                      | 0.0                              |

| 7.7                                    | applications                                                                                                                                                                                                                                                                                                                                                                                                  | 96                               |

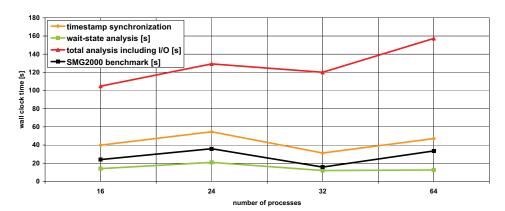

| 7.8                                    | Normalized execution time on Nicole                                                                                                                                                                                                                                                                                                                                                                           | 100                              |

| 7.9                                    | Message statistics before and after applying the CLC algorithm on the NGS grid                                                                                                                                                                                                                                                                                                                                | 101                              |

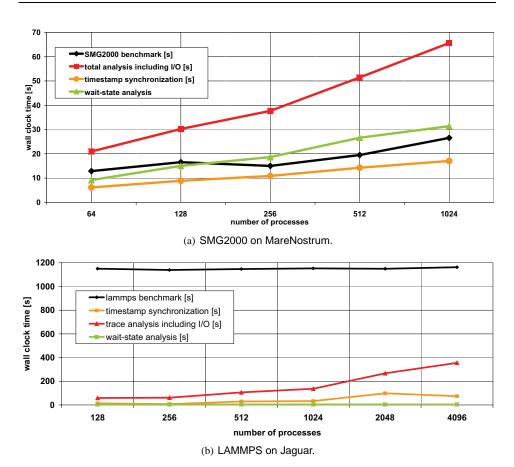

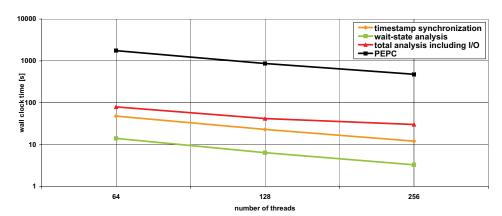

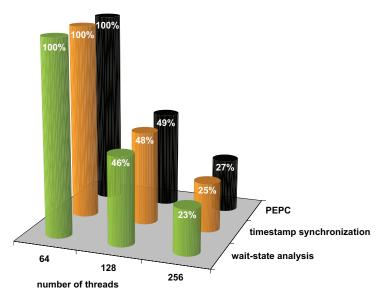

| 7.10                                   | Scalability of the parallel timestamp synchronization and SMG2000 bench-                                                                                                                                                                                                                                                                                                                                      | 101                              |

|                                        | mark on the NGS grid                                                                                                                                                                                                                                                                                                                                                                                          | 103                              |

# **List of Tables**

| 1.1        | Event attributes of Scalasca's event types.                                                                                 | 10       |

|------------|-----------------------------------------------------------------------------------------------------------------------------|----------|

| 2.1        | Xeon cluster: Process pinning for measurements among SMP nodes, chips,                                                      | 25       |

| 2.2        | and cores                                                                                                                   | 26       |

| 4.1<br>4.2 | Event sequences recorded for typical MPI operations                                                                         | 42<br>43 |

| 5.1<br>5.2 | Classification of MPI collective communication                                                                              | 52<br>55 |

| 6.1        | Timestamps exchanged among communication peers during forward replay                                                        |          |

| 6.2        | for different message-passing communication types                                                                           | 68<br>70 |

| 6.3        | Timestamps exchanged among communication peers during the two replay phases for different shared-memory communication types | 75       |

| 7.1        | Latencies of the internal and external networks in Viola                                                                    | 86       |

| 7.2        | Number of clock condition violations                                                                                        | 87       |

| 7.3        | Average and maximum errors for SMG2000 and LAMMPS                                                                           | 91       |

| 7.4        | SMG2000: Relative deviation of the event distance                                                                           | 92       |

| 7.5        | LAMMPS: Relative deviation of the event distance                                                                            | 93       |

| 7.6        | Distribution of reversed messages and violated messages detected during the                                                 |          |

| 77         | timestamp synchronization on Nicole.                                                                                        | 95       |

| 7.7        | Average and maximum errors of message events in reversed order on Nicole.                                                   | 97       |

| 7.8        | Relative deviation of the event distance on Nicole                                                                          | 98       |

| 7.9        | Relative deviation of the event distance on the NGS grid.                                                                   | 102      |

# Chapter 1

## Introduction

Supercomputing is a key technological pillar of modern science and engineering, indispensable for solving critical problems of high complexity. World-wide efforts to build machines with performance levels in the petaflops range acknowledge that the requirements of many key applications can only be met by the most advanced custom-designed large-scale computer systems. However, as a prerequisite for their productive use, the HPC community needs powerful and robust software tools that make the development of parallel applications both more effective and more efficient. Such tools not only help to improve the scalability characteristics of scientific codes and thus expand their potential, but also allow domain experts to concentrate on the science underneath rather than to spend a major fraction of their time debugging their code and tuning it for a particular machine.

## 1.1 Parallel Computers

Todays supercomputers are most commonly parallel computers, executing one program on multiple processors in parallel and so jointly computing the solution of a large scientific or technical problem. Often, such parallel computers are classified based on the memory architecture and referred to as shared-memory or distributed-memory architectures [48]. On shared-memory machines, all processors share a common address space, whereas distributedmemory machines exhibit multiple private address spaces. Shared-memory architectures are classified as either symmetric shared-memory or distributed shared-memory multiprocessors. Symmetric shared-memory multiprocessors (SMP) have a symmetric relationship to memory and include systems like SUN Sunfire or IBM eserver nodes [48]. This style of architecture is also called uniform memory access (UMA), arising from the fact that all processors have a uniform latency to memory. Architectures that support shared memory in a distributed fashion are called distributed shared-memory (DSM) multiprocessors. Such distributed sharedmemory architectures have variable access times to a memory address and are called nonuniform memory access (NUMA). In addition, cache coherent non-uniform memory access (ccNUMA) architectures, such as SGI Origin/Altix, are similar to NUMA architectures but use protocols to guarantee cache coherence across the machine.

In contrast, distributed-memory architectures, often referred to as *massively parallel processors* (MPP), do not provide a common address space but provide interconnection networks to exchange data among processors. The data exchange is typically done by sending and

#### 1. INTRODUCTION

**Figure 1.1:** Schematic view of a cluster with multiple nodes and its interconnection network.

receiving messages between communication peers, since each network node has its own local memory which is not accessible from another processor. Parallel computers that use this message-passing approach are called clusters. The individual nodes of a cluster are either commodities or customized, likewise the interconnection network. The nodes and networks of a commodity cluster are usually standard components, whereas the nodes and the interconnect of a custom cluster are customized and more tightly integrated than in a commodity cluster. Typical representatives of custom clusters are IBM Blue Gene and Cray XT systems. Driven by the availability of inexpensive commodity components produced in large quantities, commodity clusters now represent the majority of supercomputing systems, exhibiting a vast diversity in terms of architecture, interconnect technology, and software environment. Commodity clusters include, but are not restricted to, Beowulf-class PC clusters which are composed of commodity hardware, a dedicated interconnection network, and an open-source software stack [30]. Often, these systems are also referred to as Linux clusters or PC clusters. A Beowulf that is built entirely using commodity components is referred to as Class I, whereas Class II clusters may use commodity components along with specialized hardware [87]. In addition, commodity clusters also include other "homemade" clusters [48], for instance, consisting of locally dispersed workstations (e.g., in different offices) linked by a local-area network. Finally, a single cluster node usually consists of many processors sharing a common address space and so clusters may be regarded as coupled SMP systems. Figure 1.1 shows the schematic view of a cluster with multiple nodes and its interconnection network.

Nowadays, clusters represent the majority of supercomputer systems because a low development effort and cheap standard components make their use popular [48]. Given that the processors of a cluster use the interconnection network for exchanging data among processors, the network performance has a major influence on the overall performance of the system. Therefore, different types of networks are used on a cluster in order to increase its performance. On-chip networks are used for interconnecting functional units, caches, and processors within chips or multichip devices. System-area networks are used for interprocessor and processor-memory interconnections within parallel computers. In contrast to custom-built solutions (e.g., IBM Blue Gene and Cray XT), commodity clusters often leverage InfiniBand and Myrinet networks [55, 70]. Finally, local-area networks (LAN) usually connect computer

systems within a single building, whereas wide-area networks (WAN) connect geographically dispersed computers.

Operating systems are used to manage the resources of a parallel computer such as the CPUs, main memory, and network [86]. On shared-memory architectures, one operating system image manages all hardware resources including all the CPUs and the shared memory. In contrast, on distributed memory architectures, each processor typically runs its own OS kernel managing local resources such as the local CPU and memory. In addition, each processor runs further software modules supporting distributed operating system services such as the handling of interprocessor communication. Note that the processor-local operating system may also use globally accessible modules responsible for centralized services (e.g., file-system services or batch system).

## 1.2 Programming Models

In order to parallelize programs, different parallel programming models are available. Similar to the classification of parallel computers, parallel programming models are classified either as multithreading or as message-passing models [23, 90]. In a multithreading model, one parallel program is concurrently executed by many threads representing execution states that are able to process an instruction stream. As all threads can access the same memory, data exchange among threads is done via shared-memory variables. Synchronization mechanisms, such as locking specific variables or barrier constructs, are used to avoid race conditions. For instance, OpenMP (Open specifications for Multi Processing) [75] is a widespread programming interface realizing a multithreading programming model. It assumes that one master thread creates a team of worker threads once a parallel region has been entered and terminates it after the parallel region has been left. OpenMP provides directives and library calls to coordinate the accesses to shared data, ensuring that certain operations are performed by only one thread at a time.

The programming model on distributed-memory systems is referred to as message passing. This model assumes that programs are executed by one or more processes, each of which has its own private address space. For instance, the MPI (Message Passing Interface) [66] communication library defines a de-facto standard for message passing and is available on most parallel computers. MPI provides means to execute multiple processes in parallel, along with operations for sending and receiving messages, and for performing collective operations across data distributed among different processes. The latest version, MPI 2.1, additionally supports parallel I/O and one-sided communication assuming that a process may interact directly with remote memory across a network to read and write data anywhere on a machine.

Parallel programs can also use message passing and multithreading in combination. Such programs are often referred to as *hybrid* programs. In particular, MPI and OpenMP may be used together in a program, typically on MPPs that consist of multiple SMPs. In such a hybrid programming model, each thread can issue MPI calls. However, MPI may be implemented in environments where threads are not supported or perform poorly, and therefore, it is not required that an MPI implementation fulfills the above requirement. For this reason, MPI

#### 1. INTRODUCTION

**Figure 1.2:** Schematic view of a metacomputer including its external and internal networks.

provides software functions to query the respective level of thread support. If only one thread is allowed to be executed at a time, the thread level is *single*. Once multiple threads per process are allowed, the thread level may be *funneled*, *serialized*, or *multiple*. In funneled mode, only the master thread makes MPI calls, whereas in serialized mode all threads make MPI calls but never concurrently. Finally, if multiple threads can make MPI calls without restrictions, the thread level is called multiple.

# 1.3 Metacomputing Environments

Often, the solution of compute-intensive problems requires more processing power than is available on a single cluster because the problem cannot be solved within a reasonable time frame on a single machine or because the solution must be calculated under real-time conditions. For this reason, the processing power and memory capacity of multiple clusters can be combined to form a more powerful *metacomputer* [84] that appears to its users as a single coherent system. Such a metacomputer usually consists of several independent and potentially heterogeneous and geographically dispersed clusters (metahosts), which are connected by network links to a single unit. Figure 1.2 shows the schematic view of a metacomputer, in which metahosts are internally connected via local area networks, whereas distant metahosts, which often belong to different organizations, are linked by a wide-area interconnection. In this sense, a metacomputing environment can be regarded as a special type

of computational grid. Due to their distributed nature, the predominant programming model for metacomputers is message passing, which may be combined with multithreading used within the nodes of a metahost. Apart from being a pure aggregation of computational power, such a metacomputer can also provide a suitable platform for multi-physics simulations, where the different submodels may be optimized for different architectures.

However, although applications can benefit from the increased parallelism offered by a metacomputer, as supported by a recent study by Wong and Goscinski [95], achieving satisfactory application performance is difficult. Often, applications have to deal with a hierarchy of latencies and bandwidths. In general, the heterogeneity of metahost hardware including differences in networks and architectures complicate load balancing. Given the fact that performance optimization for a single cluster is already a non-trivial task that requires substantial tool support, we can argue that this is even more important for metacomputing environments.

## 1.4 Event Tracing

Software tools are necessary to investigate the runtime behavior of parallel programs. Given that a computer changes its state in discrete intervals, it is possible to model the runtime behavior of a single program as a sequence of state changes. A single state change can be regarded as an *event* happening at a given time and location. *Event tracing* regards the execution of a program as a sequence of events, each with an associated *event type* (e.g., entering a code region). Such an event type is defined by a set of attributes (e.g., timestamp, location) that may be shared by multiple event types depending on the level of specialization. An *event model* defines the event types with their related attributes and constraints, for example, regarding the correct event order. Obviously, the selection of event types observed determines the expressiveness and granularity an event trace can provide.

Event tracing is a widely used technique by software tools with a broad spectrum of applications ranging from debugging, performance modeling and prediction to performance analysis. For instance, as programming user-defined process topologies is often error-prone, Huband et al. [53] describe a trace-based topology debugger that exploits topological information to abstract, identify, and report patterns of expected and unexpected communication behavior. In addition, performance models can be derived from event traces and subsequently used for performance prediction. Labarta et al. [60] determine such performance models as functions of specific parameters such as the processor count or speed and the network latency or bandwidth. Based on event traces taken on a small number of processors, Rodriguez et al. [82] use these performance models to predict the program performance when running on a large number of processors, enabling the tuning of message-passing programs before actually running them on those large configurations.

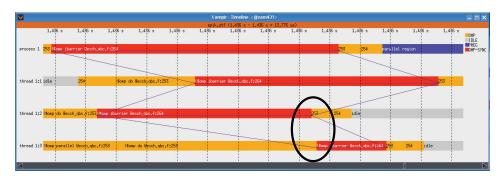

Moreover, event traces can be searched for potential performance bottlenecks either manually or automatically [90]. Manual trace analysis transforms event traces into a visual representation of the runtime behavior, which can be interactively explored in graphical trace browsers such as Vampir [71] and Paraver [60]. These trace browsers allow the fine-grained investigation of an application's runtime behavior and provide statistical summaries, translating a

#### 1. INTRODUCTION

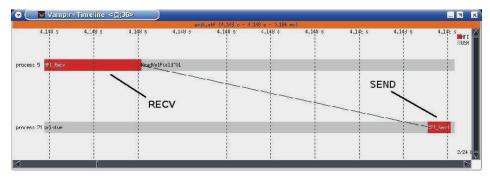

**Figure 1.3:** Graphical trace browser Vampir: Time-line visualization of an application's runtime behavior.

given event trace into a variety of graphical views including state diagrams, activity charts, and zoomable time-line displays. Figure 1.3 shows a time-line visualization of an application running with 24 processes. Such a time-line visualization consists of boxes indicating the execution of different code sections, arrows indicating point-to-point communication, and dashed lines indicating collective communication. Here, the time spent in MPI calls is visualized through red boxes, whereas the time spent in user regions is visualized through grey boxes. In addition, point-to-point messages are shown with black arrows, whereas collective communication is shown with purple dashed lines. As a consequence, developers can easily identify different execution and communication phases of the application. Using the zooming functionality, they can subsequently investigate the runtime behavior at any level of granularity in or between those phases. However, in view of the large amounts of data generated on contemporary parallel computers, performance bottlenecks can be identified more efficiently by automatically searching the trace data for their occurrence. In addition to usually being faster than a manual analysis performed using a trace browser, this approach is also guaranteed to cover the entire event trace and not to miss any instances.

Automatic trace analysis transforms the event trace into a compact representation of the performance behavior in terms of inefficiency patterns. For instance, the KOJAK [93] and Scalasca [92] toolset automatically search event traces of parallel programs for patterns of inefficient behavior, classify detected instances by category, and quantify the associated performance penalty. This allows developers to study the performance of their applications on a higher level of abstraction, while requiring significantly less time and expertise than a manual analysis. A distinctive feature of both tools is their ability to identify wait states that potentially occur as a result of unevenly distributed workloads. Especially when trying to scale communication intensive applications to large processor counts, such wait states can

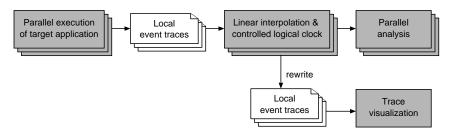

**Figure 1.4:** Schematic overview of the performance data flow in Scalasca. Grey rectangles denote programs and white rectangles with the upper right corner turned down denote files. Stacked symbols denote multiple instances of programs, files, or data objects running or being processed in parallel.

present severe challenges to achieving good performance. Given that KOJAK analyzes a single global trace file sequentially, its processing scheme is limited as soon as it targets traces taken on such large processor counts. In view of rapidly increasing parallelism, it is crucial that the trace analysis scales to large numbers of application processes [19, 22, 44]. In addition, exponentially rising numbers of cores and increased concurrency levels place even higher scalability demands on this trace analysis [73, 88]. As KOJAK's successor, Scalasca has been specifically designed for use on large-scale systems including IBM Blue Gene and Cray XT, but is also well-suited for small- and medium-scale clusters. Instead of sequentially processing a single global trace file, Scalasca implements a scalable trace-analysis approach [44] by processing separate process-local trace files in parallel and *replaying* the original communication on as many CPUs as were used to execute the target application itself. Since trace processing capabilities (i.e., processors and memory) grow proportionally with the number of application processes, this approach guarantees good scalability at very large scales.

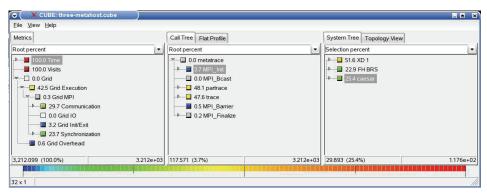

Scalasca supports an incremental performance analysis process that integrates runtime summaries with in-depth studies of concurrent behavior via event tracing, adopting a strategy of successively refined measurement configurations. Figure 1.4 shows the basic analysis workflow supported by Scalasca. Before any performance data can be collected, the target application must be instrumented. When running the instrumented code on the parallel machine, the user can choose to generate a summary report ("profile") with aggregate performance metrics for individual function call paths, and/or event traces recording individual runtime events from which a profile can later be produced. Summarization is particularly useful to obtain an overview of the performance behavior and for local metrics such as those derived from hardware counters [18]. Since traces tend to rapidly become very large, scoring of a summary report is usually recommended, as this allows instrumentation and measurement to be optimized. When tracing is enabled, each process generates a trace file containing records for its process-local events. After program termination, Scalasca loads the trace files into main memory and searches them in parallel for patterns of inefficient performance behavior using the above-mentioned replay mechanism. The result is a trace-analysis report similar in structure to the summary report but enriched with higher-level communication and synchronization inefficiency metrics. Both summary and trace-analysis reports contain performance metrics for every function call path and process/thread which can be interactively

#### 1. INTRODUCTION

Figure 1.5: Scalasca's trace-analysis report.

examined in the provided analysis-report browser shown in Figure 1.5. The tree in the left window pane displays patterns of inefficient performance behavior arranged in a specialization hierarchy. In addition, the middle window pane shows the distribution of the selected pattern's severity across the call tree. Finally, the right window pane shows the distribution of the pattern's severity at the selected call path across the machine topology.

When an application is traced, runtime events critical to communication and computation activities are intercepted and temporarily stored in main memory. These performance-relevant events are subsequently written to a trace file according to the Scalasca event model. Performance-relevant events include entering and leaving functions or other code regions as well as sending and receiving point-to-point messages or participation in collective communication. Whereas the communication-related event types are crucial to study the interactions among different processors and to identify wait states, function entries and exits are needed to understand the computational requirements and the context in which the most demanding communication operations occur.

Table 1.1: Event types of the Scalasca event model as used in this thesis.

| Name                       | Description                               | Abbr. |  |  |  |  |

|----------------------------|-------------------------------------------|-------|--|--|--|--|

| Programming-model inde     | Programming-model independent event types |       |  |  |  |  |

| Enter                      | Region entered                            | Е     |  |  |  |  |

| Exit                       | Region left                               | X     |  |  |  |  |

| MPI-related event types    |                                           |       |  |  |  |  |

| Send                       | Message sent                              | S     |  |  |  |  |

| Receive                    | Message received                          | R     |  |  |  |  |

| MPI Collective Exit        | MPI collective code region left           | MX    |  |  |  |  |

| OpenMP-related event types |                                           |       |  |  |  |  |

| Fork                       | Master thread creates a team of threads   | F     |  |  |  |  |

| Join                       | Worker threads finish their execution     | J     |  |  |  |  |

| OpenMP Collective Exit     | OpenMP collective code region left        | OX    |  |  |  |  |

| Lock-Acquisition           | Lock variable acquired                    | L     |  |  |  |  |

| Lock-Release               | Lock variable released                    | U     |  |  |  |  |

Given that this thesis focuses on a synchronization method to be used within Scalasca, the Scalasca event model is described in more detail. The Scalasca event model has been designed to provide a uniform data representation suitable for MPI, OpenMP, and hybrid applications that use MPI and OpenMP in combination. The model maps events onto their location within the hierarchical hardware (i.e., machine and node) and to their process and thread of execution. It supports the storage of all necessary source code and call-site information, recording of performance metrics, such as hardware counters [18], and marking of collectively executed operations for both MPI and OpenMP. For the tracing of OpenMP-related events, Scalasca uses the POMP performance interface [69] and assumes that the same team of threads is used throughout the entire execution in funneled mode. As tracing of OpenMP ordered, task, and taskwait sections is not supported within Scalasca, it does also not account for OpenMP nested and task parallelism. In addition to clusters, target systems can also be metacomputing environments [12].

The information Scalasca records for an individual event includes at least the timestamp, the location (i.e., the process or thread) causing the event, and the event type. Depending on the type, additional information may be supplied. The event model distinguishes between programming-model independent events and events related to MPI operations and OpenMP constructs. Table 1.1 lists all programming-model independent as well as MPI- and OpenMP-related event types of the Scalasca event model [94] along with a brief explanation and their abbreviation as used in this thesis. In addition, Table 1.2 lists the event attributes for each event type.

Programming-model independent events indicate that a program enters or leaves a code region. Such a code region of a parallel program may be a function, a loop, or just a basic block [90]. One execution of a region forms a region instance. As a consistency requirement, regions must be left in the reverse order they are entered. That is, the region that has been entered last at a location must be left first on that location. Figure 1.6 illustrates typical event sequences

Table 1.2: Event attributes of Scalasca's event types.

| Event type                                | Event type attributes              |

|-------------------------------------------|------------------------------------|

| General attributes for all event types    |                                    |

|                                           | Location                           |

|                                           | Timestamp                          |

| Programming-model independent event types |                                    |

| Enter                                     | Region entered                     |

|                                           | Hardware counter values (optional) |

| Exit                                      | Region exited                      |

|                                           | Hardware counter values (optional) |

| MPI-related event types                   |                                    |

| Send                                      | Destination location of message    |

|                                           | Communicator                       |

|                                           | Message tag                        |

|                                           | Message length in bytes            |

| Recv                                      | Source location of message         |

|                                           | Communicator                       |

|                                           | Message tag                        |

|                                           | Message length in bytes            |

| MPI Collective Exit                       | Collective region left             |

|                                           | Root location of the operation     |

|                                           | Communicator                       |

|                                           | Bytes sent                         |

|                                           | Bytes received                     |

|                                           | Hardware counter values (optional) |

| OpenMP-related event types                |                                    |

| Join                                      |                                    |

| Fork                                      |                                    |

| Lock-Acquisition                          | Lock variable acquired             |

| Lock-Release                              | Lock variable released             |

| OpenMP Collective Exit                    | Collective region left             |

|                                           | Hardware counter values (optional) |

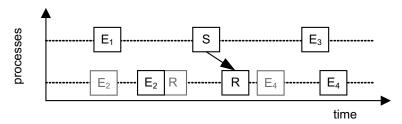

according to the Scalasca event model exemplified with the time lines of two locations (i.e., processes or threads). For example, Figure 1.6(a) shows the event sequences of user code region instances consisting of an enter  $(E_i)$  and exit  $(X_i)$  event record on each location.

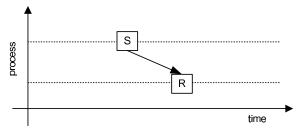

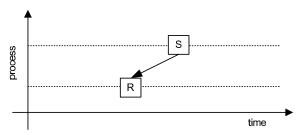

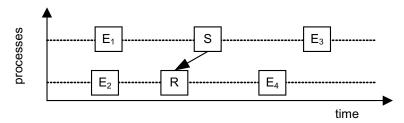

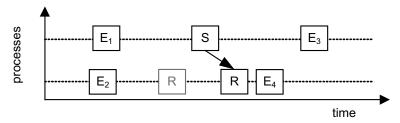

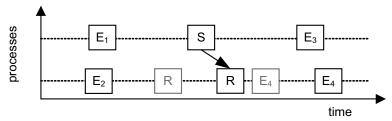

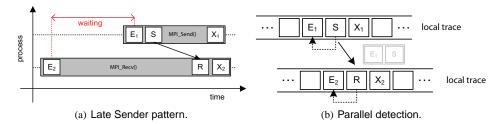

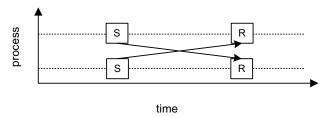

Moreover, MPI-related events include events representing point-to-point operations, such as sending and receiving messages, and events representing the completion of MPI collective operations. Figure 1.6(b) shows a point-to-point message exchange between two locations. The respective send (S) and receive (R) event records are enclosed by enter  $(E_i)$  and exit  $(X_i)$  event records indicating that a sending or receiving region has been entered or left. Here, the MPI message semantics in combination with event attributes (e.g., destination location, source location) enable the determination of the correct logical event sequence. Note that the send

Figure 1.6: Typical event sequences according to the Scalasca event model.

event always marks the beginning of a send operation, whereas a receive event marks the end of a receive operation. Assuming globally synchronized clocks, this scheme guarantees that the timestamp of the receive event is larger than the timestamp of the send event. In addition, Figure 1.6(c) presents a collective operation instance, on each location marked by enter  $(E_i)$  and collective exit  $(MX_i)$  event records. These collective exit events are specializations of normal exit events carrying, among other attributes, information on the communicator. This information allows identifying concurrent collective exits belonging to the same collective operation instance.

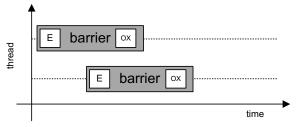

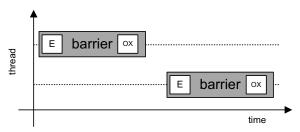

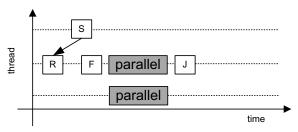

Finally, OpenMP-related events include events that represent the creation and termination of a team of threads, leaving parallel regions or barriers executed in parallel, and acquiring and releasing lock variables. As can be seen in Figure 1.6(d), a fork (F) event record indicates that the master thread creates a team of threads, whereas a join (J) event record indicates that this team of threads is terminated. The location of both events is always the location of the master thread. In this situation, the enter  $(E_i)$  event records indicate that a program enters a parallel region, whereas the OpenMP-related collective exit  $(OX_i)$  event records indicate that the program leaves the parallel region.

Figure 1.7 shows typical event sequences inside OpenMP parallel regions with the time lines of two locations (i.e., threads). For the sake of simplicity, fork and join event records are left out. Figure 1.7(a) presents an OpenMP barrier instance, on each location enclosed by an enter  $(E_i)$  and OpenMP collective exit  $(OX_i)$  event record. In addition, lock event semantics are illustrated in Figure 1.7(b). The respective lock-acquisition (L) and lock-release (U) event records are enclosed by enter  $(E_i)$  and exit  $(X_i)$  event records indicating that a thread entered or left an omp\_set\_lock or omp\_unset\_lock region. Whereas the lock-acquisition (L) event record indicates that a lock variable is acquired by a thread (i.e., shared variable locked), the lock-release (U) event record indicates that this lock is released (i.e., shared variable unlocked). In the Scalasca event model, the correct sequence of lock events is only given by the timestamp of the respective events. Assuming that the thread-local clocks are synchronized,

#### 1. INTRODUCTION

**Figure 1.7:** Typical event sequences inside OpenMP parallel regions according to the Scalasca event model.

the timestamp could be used to determine the logical sequence of locks during the program run. However, on some systems this assumption cannot be maintained and so a further global event attribute, such as a sequence count which is incremented once a lock is acquired, is necessary to decide which thread acquires a lock after another thread has released it. So far, the Scalasca event model does not provide such an attribute. Note that the lock-acquisition (L) event record always marks the end of an set-lock operation, whereas the lock-release (U) event record marks the beginning of the unset-lock operation. Given that a critical construct restricts the execution of a structured block to a single thread at a time, the Scalasca event model uses lock-acquisition and lock-release event records to indicate when the associated structured block was locked or unlocked. Both events are recorded inside the critical section: the lock-acquisition event record at the beginning and the lock-release event record at the end. More specifically, as can be seen in Figure 1.7(c), before the structured block of the critical region is entered ( $E_i$  event records) it is locked ( $L_i$  event records), and is again unlocked  $(U_i)$  after the structured block is left  $(X_i \text{ event records})$ . Finally, only one thread is allowed to execute an OpenMP atomic construct at a time (see Figure 1.7(d)). In general, an atomic region is only described by enter  $(E_i)$  event records and exit  $(X_i)$  event records. However, these events are recorded before the region was entered and after the region was left because tracing inside such a region is not possible. To determine which thread executed the atomic region before another thread, it would be necessary to record when a thread executes the atomic region. Unfortunately, the execution of an atomic region is restricted to statements that can be calculated atomically and so it is not possible to insert event tracing calls. Note that tracing inside atomic regions would be inefficient, because it would impose a large and non-negligible overhead.

Figure 1.8: Time-line visualization of a message exchange in backward direction.

#### 1.5 Timestamp Synchronization

In general, the accuracy of trace analysis depends on the comparability of timestamps taken on different processors. Inaccurate timestamps may cause a given interval to appear shorter or longer than it actually was, or change the logical event order, which requires a message to be received only after it has been sent. This is also referred to as the *clock condition*. Inaccurate timestamps may lead to false conclusions during performance analysis, for example, when the impact of certain behaviors is quantified, or – even more strikingly – may confuse the user of trace-visualization tools such as Vampir by causing arrows representing messages to point backward in time-line views (see Figure 1.8). Moreover, tools such as KOJAK may also cease to work in a satisfactory manner if they rely on message event orders imposed by the communication substrate to which an operation belongs.

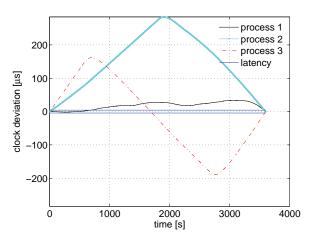

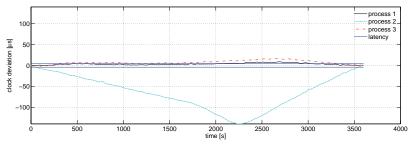

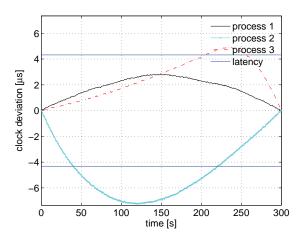

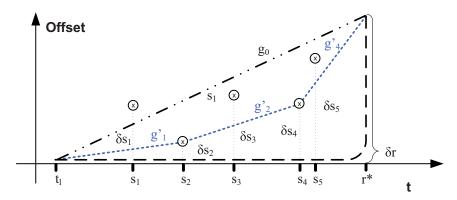

To avoid clock condition violations, the error of timestamps should ideally be smaller than one half of the message latency  $\mu$ . For instance, let us assume that a send event appears  $\frac{1}{2}\mu$  too early while the matching receive event appears  $\frac{1}{2}\mu$  too late in the trace. If we now consider a message delay of exactly the message latency, the send event appears at the same time as the matching receive event does, which is impossible and considered a clock condition violation. While some custom-built clusters such as IBM Blue Gene offer relatively accurate global clocks, most commodity clusters provide only processor-local clocks that are either entirely non-synchronized or synchronized only within disjoint partitions (e.g., SMP node). Clock synchronization protocols such as NTP [68] can align the clocks to a certain degree, but are often not accurate enough for the purposes of program observation. Assuming that every local clock on a parallel machine runs at a different but constant speed (i.e., drift), the (global) time of an arbitrarily chosen master clock can be calculated locally as a linear function of the local time. For this purpose, offset measurements may be performed between all local clocks and the master clock once at program initialization and once at program finalization. However, as the assumption of constant drifts is only an approximation, violations of the clock condition may still occur - especially when the offset measurements are taken with long intervals in between. Figure 1.9 shows clock deviations after linear offset interpolation measured using a simple benchmark program that was executed for 3600 seconds on an Intel Xeon cluster.

**Figure 1.9:** Non-linear offsets of physical clocks measured on a Xeon cluster in comparison to the send-receive latency.

As can be seen, the non-linearity of local clocks caused clock errors much larger than the send-receive latency.

While the errors of single timestamps are hard to assess, clock condition violations can be easily detected and offer a toehold to increase the fidelity of inter-process and inter-thread timings. The *controlled logical clock* (CLC) [79] is a method to retroactively correct timestamps violating the clock condition. As the modification of individual event timestamps might change the length of local intervals and even introduce new violations, the correction takes the context of the modified event into account by carefully adjusting the local time axis from the immediate past of the affected event to the end of the local trace. This algorithm is, however, not suitable for realistic parallel programs because (i) it ignores collective and shared-memory communication and (ii) as a serial algorithm it offers only limited scalability. The original CLC algorithm cannot be used to correct clock condition violations among MPI collective events and OpenMP events. Even more strikingly, the algorithm may introduce new violations because it ignores happened-before relations among MPI collective events and OpenMP events while correcting point-to-point event semantics.

Focusing onto cluster systems but not losing sight of the more general metacomputing case, the contribution of this thesis is fourfold:

- The thesis investigates the robustness of linear offset interpolation across a range of timer technologies available on different platforms and shows that the error of timestamps derived in this way can easily compromise the consistency of the logical event order imposed by the event semantics.

- 2. This thesis extends the algorithm to enable the correction of realistic traces taken from MPI and hybrid applications. The basic idea behind the extension is to consider

- collective and shared-memory operations as being composed of multiple point-to-point messages, taking the semantics of the different flavors of operations into account.

- 3. To accomplish this correction in a scalable way, both distributed memory and parallel processing capabilities are exploited by processing separate local trace files in parallel and replaying the original communication on as many CPUs as were used to execute the target application itself.

- 4. To employ the replay mechanism in computational grids, this work also defines the necessary infrastructure to accurately measure clock offsets in distributed environments based on hierarchical networks.

The remainder of this thesis is structured as follows: Chapter 2 starts with a description of the most common clock types and their accessibility, followed by the investigation of the robustness of linear offset interpolation including the influence on timestamps of concurrent events. While Chapter 3 reviews related work in general, Chapter 4 introduces the original serial version of the CLC algorithm including its limitations in more detail. In Chapter 5, the extensions necessary to correctly synchronize collective and shared-memory operations are introduced. Then, Chapter 6 presents the parallel algorithm design and describes its implementation within Scalasca. Chapter 7 evaluates the scalability of the parallel version, and also shows that the collaterally introduced deviations of local interval lengths remain within acceptable limits. Finally, Chapter 8 summarizes the thesis research and outlines future work.

## 1. INTRODUCTION

# Chapter 2

# **Processor Clocks**

Measuring the time between concurrent events requires a global clock, which is often unavailable on clusters. Assuming that the potentially different drifts of local clocks remain constant over time, linear offset interpolation can be applied postmortem to map local timestamps onto global timestamps. In this chapter, the robustness of the above assumption is investigated using different types of timers. It is shown that the error of timestamps derived in this way can easily lead to a misrepresentation of the logical event order imposed by the semantics of the underlying communication substrate. This indicates that linear offset interpolation alone may be insufficient for many applications of event tracing.

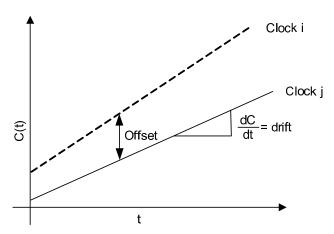

### 2.1 Classification

Processor clocks are used to obtain event timestamps and can be characterized in terms of their relative offset and drift. The clock offset is the time difference between two clocks at a given time, whereas the clock drift is the rate at which a clock progresses over time, which may also be different for two clocks. Figure 2.1 shows two clocks with both an initial offset and different but constant drifts. Assuming that clocks have different but constant drifts, the (global) time of an arbitrarily chosen master clock can be calculated locally as a linear function of the local time. However, the rate at which the offset changes over time (i.e., clock drift) is usually time dependent. Given that different clock types may exhibit different offset and drift characteristics, this section reviews the most common clock types and explains how they can be accessed [9].

### 2.1.1 Clock Types

Different types of clocks are used to measure and maintain the processor time. Clocks based on cycle counters use the processor clock signal to increment an internal counter on each tick. The step size, which depends on the clock rate, may change over time, as state-of-the-art power management may dynamically slow down or accelerate the signal. As a consequence, remote cycle counters are very hard to synchronize and therefore only useful to compare events happening on the same CPU.

In contrast, hardware clocks, often called timestamp counters, use specialized hardware counters. Based on separate oscillators, their values are incremented on each tick of the

Figure 2.1: Two clocks with both an initial offset and different but constant drifts.

oscillator, and thus, their step size does not depend on a potentially unstable processor clock rate. Although a single hardware clock can provide accurate relative timings, synchronization among multiple remote hardware clocks is usually not provided.

As another alternative, software clocks are realized in the form of user or library functions. Often, those clocks are implemented entirely in software without any dedicated hardware support. Software-based synchronization among different software clocks (e.g., via NTP) may guarantee synchronized time values to a certain degree [67].

Finally, system clocks are specializations of software clocks and managed by the operating system (e.g., gettimeofday()). Such system clocks are usually based on cycle counters, hardware clocks, or software clocks and maintain the system-local time.

As examples of hardware clocks, we consider IBM's real-time clock (RTC), IBM's time base register (TB), and Intel's timestamp counter register (TSC). All these clocks are 64-bit special-purpose registers. RTC counts seconds and nanoseconds, while TB and TSC return the number of ticks counted since processor reset. In contrast, MPI\_Wtime() must be classified as a software clock that can be used to transparently query clock values on cluster systems. Open MPI [74], a widely used open-source MPI library, chooses among a rich set of implementations for MPI\_Wtime() at configuration time. The default is gettimeofday(), which often relies on network-based synchronization via NTP [68]. The general idea behind NTP is to synchronize distributed clocks before reading them. The distributed clocks query the global time from reference clocks, which are often organized in a hierarchy of servers. NTP uses widely accessible and already synchronized primary time servers. In addition, secondary time servers and clients can query time information via both private networks and the Internet. To reduce network traffic, the time servers are accessed only in regular intervals to adjust the local clock. Jumps are avoided by changing the drift while leaving the actual time unmodified. Unfortunately, varying network latencies limit the accuracy of NTP to about one millisecond

compared to a few microseconds required to accurately trace MPI applications running on clusters equipped with modern interconnect technology [67].

### 2.1.2 Clock Accessibility